Your What is behavioral modeling in vhdl images are ready in this website. What is behavioral modeling in vhdl are a topic that is being searched for and liked by netizens today. You can Get the What is behavioral modeling in vhdl files here. Get all royalty-free photos.

If you’re looking for what is behavioral modeling in vhdl images information related to the what is behavioral modeling in vhdl keyword, you have pay a visit to the ideal blog. Our site frequently provides you with hints for viewing the highest quality video and image content, please kindly surf and locate more informative video articles and images that match your interests.

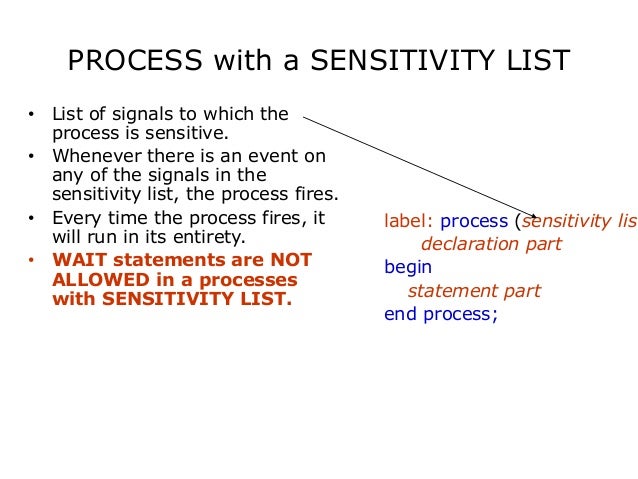

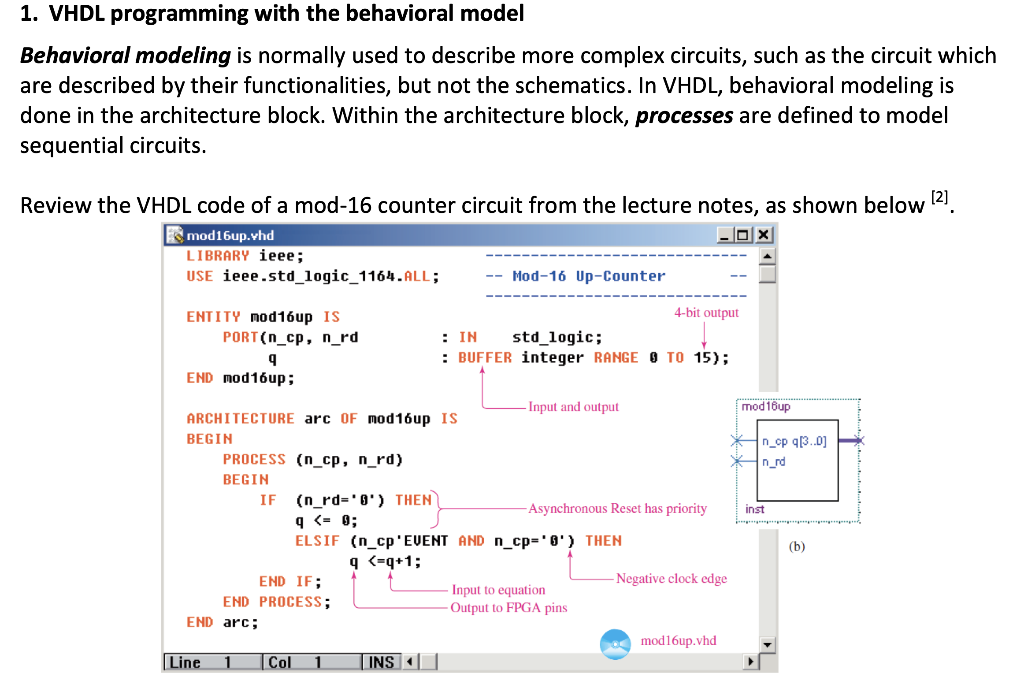

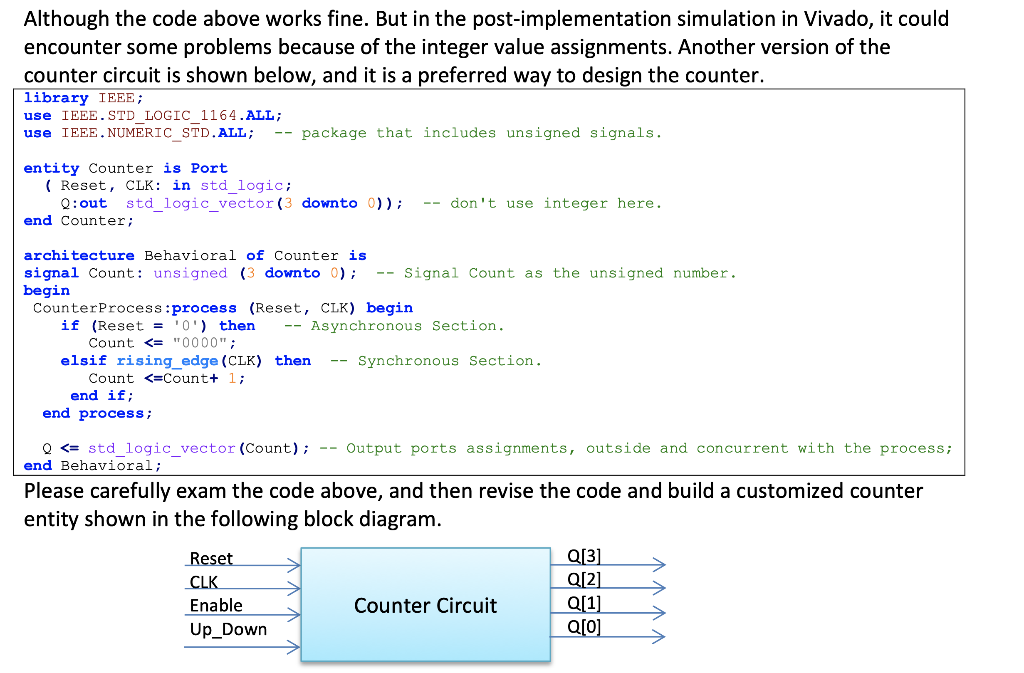

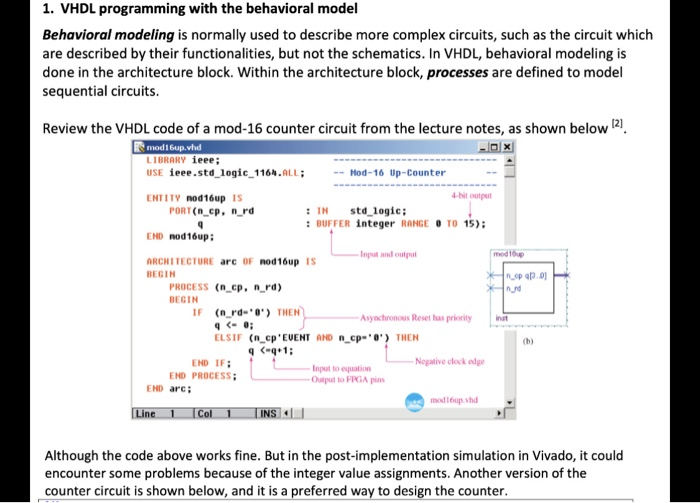

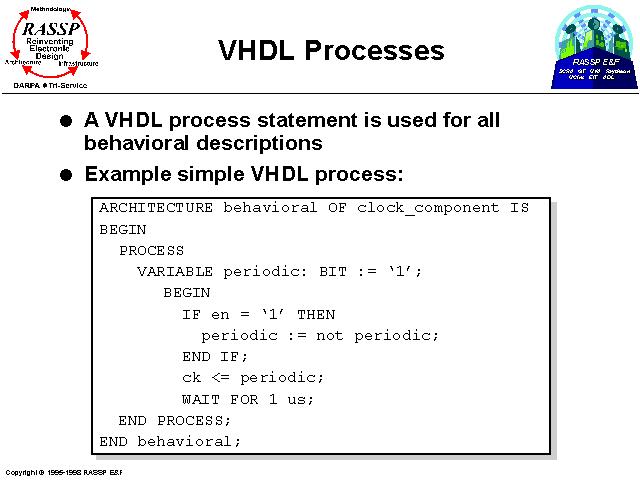

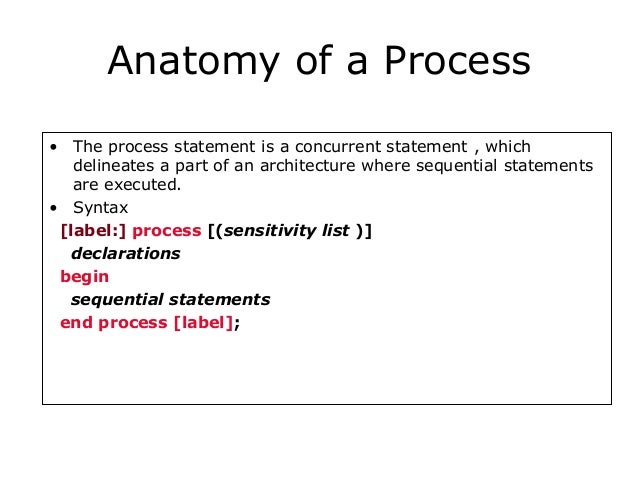

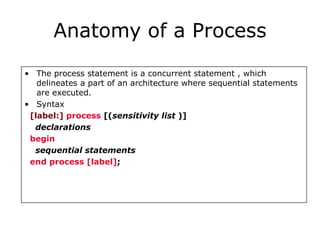

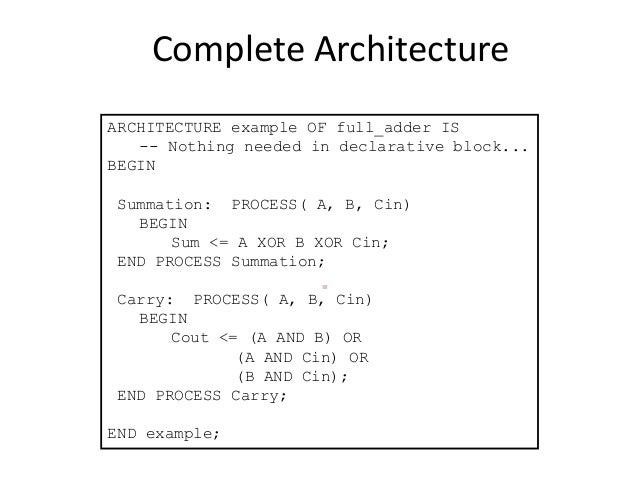

What Is Behavioral Modeling In Vhdl. 2 Behavioral Style of Modelling. Sometimes zero delay events are used to produce consistent results. Behavioral style consists of one or more process statements. For these reasons behavioral modeling is considered highest abstraction level as compared to data-flow or structural models.

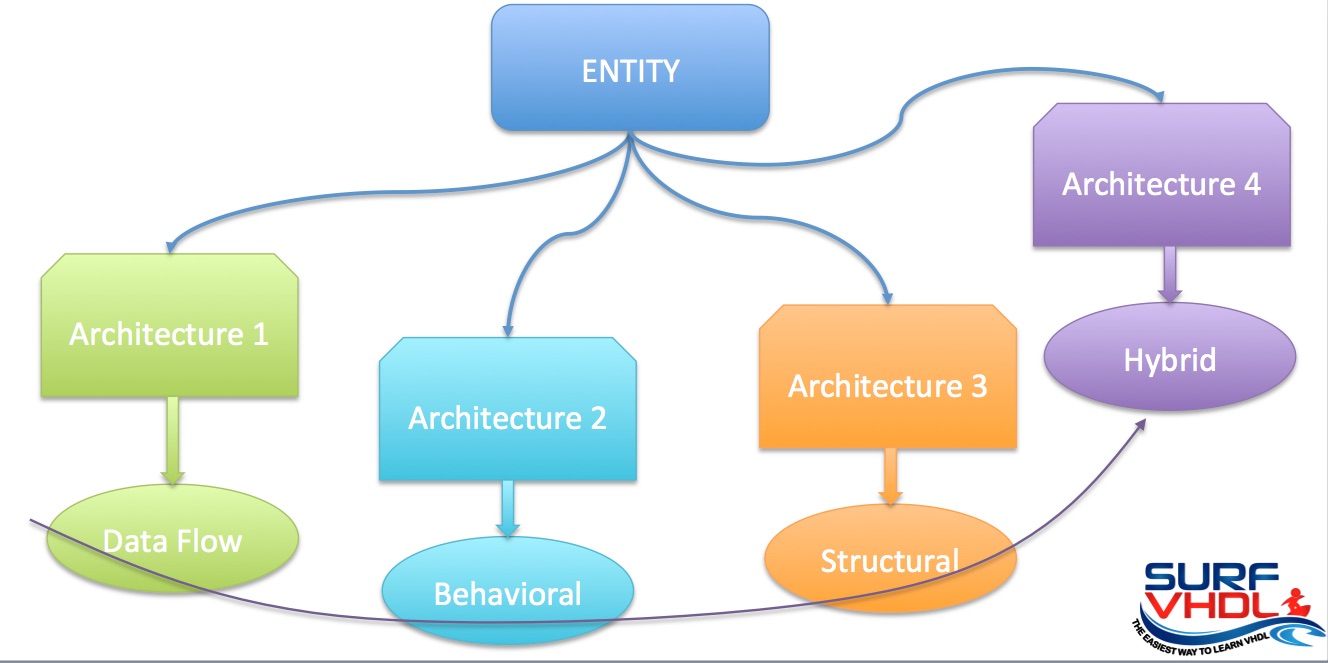

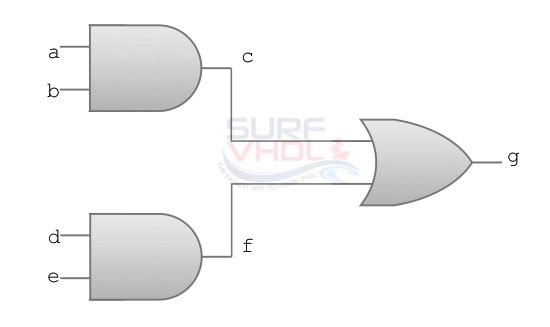

Vhdl Structural Modeling Style From surf-vhdl.com

Vhdl Structural Modeling Style From surf-vhdl.com

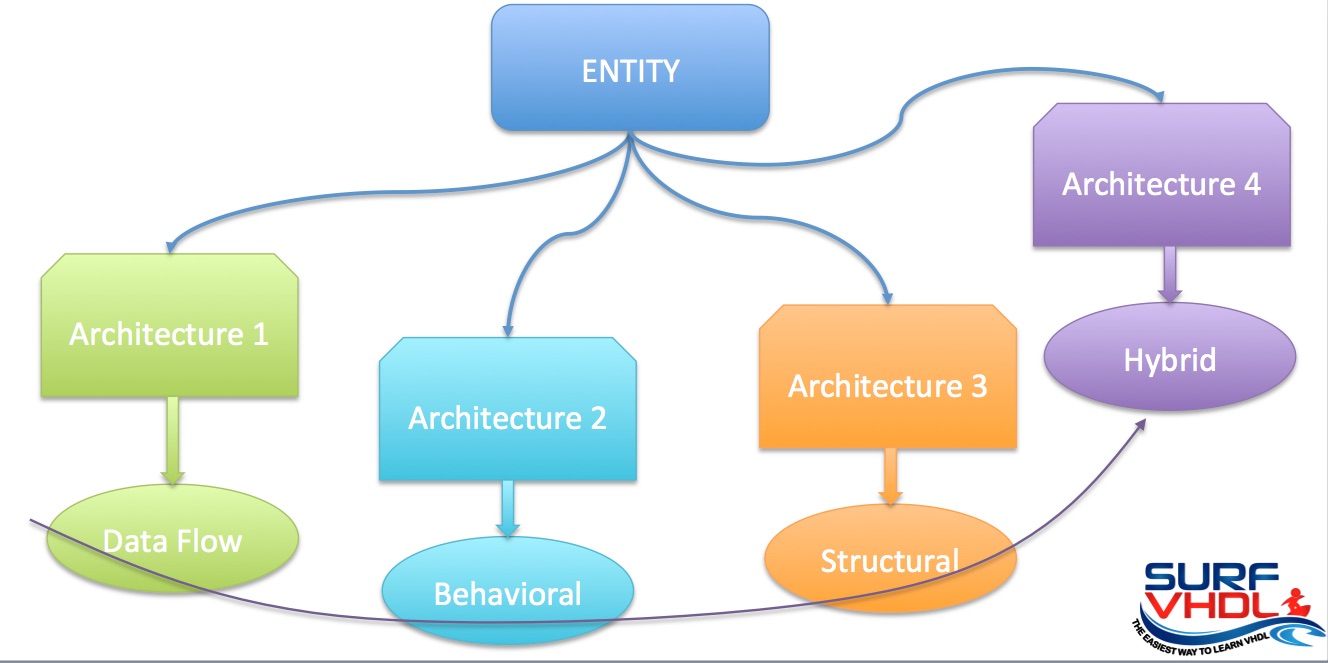

Could also include code that is completly unsynthesisable - like a bus functional model. What is the use of simulation deltas in VHDL code. The description is abstract in the sense that it does not directly imply a particular gate-level implementation. Behavioral modeling FPGA designs with VHDL documentation. In Chapter 2 and Chapter 3 we saw various elements of VHDL language along with several examplesMore specifically Chapter 2 presented various ways to design the comparator circuits ie. There are 4 types of modeling styles in VHDL.

Behavioral style consists of one or more process statements.

The VHDL synthesizer tool decides the actual circuit implementation. U uninitialised X unkown - when you drive 0 and 1 together. VHDL Design Styles VHDL Design Styles structural Components and interconnects dataflow Concurrent statements behavioral Sequential statements Registers Shift registers Counters State machines synthesizable. Sometimes zero delay events are used to produce consistent results. Data flow modeling Design Equations Data flow modeling can be described based on the Boolean expression. In the behavioral modeling style in VHDL we describe the behavior of an entity using sequential statements.

Source: technobyte.org

Source: technobyte.org

Which of the following is not a type of VHDL modeling. For simulation different levels of abstraction in VHDL you basically write a behavioral model that behaves more closely to what a structural model would. For these reasons behavioral modeling is considered highest abstraction level as compared to data-flow or structural models. It works on Concurrent execution. VHDL Design Styles VHDL Design Styles structural Components and interconnects dataflow Concurrent statements behavioral Sequential statements Registers Shift registers Counters State machines synthesizable.

Source: slideshare.net

Source: slideshare.net

Data flow modeling Design Equations Data flow modeling can be described based on the Boolean expression. Could also include code that is completly unsynthesisable - like a bus functional model. 2 Behavioral Style of Modelling. Its like writing the algorithm that solves your problem. On the other hand The Behavioral modeling in Verilog is used to describe the function of a design in an algorithmic manner so if i want to describe a 2 to 4 decoder in dataflow modeling i.

Source: chegg.com

Source: chegg.com

It shows how the data flows from input to output. In behavioral modeling there are different types of delays and this can create problem in functioning of system. It is a programming language used to model a digital system by dataflow behavioral and structural style of modeling. There are 4 types of modeling styles in VHDL. There are 4 types of modeling styles in VHDL.

Source: ece-research.unm.edu

Source: ece-research.unm.edu

The VHDL behavioral model is widely used in test bench design since the test. The VHDL synthesizer tool decides the actual circuit implementation. Behavioral DesignModelling Functional performance is the goal of behavioral modeling Timing optionally. Could also include code that is completly unsynthesisable - like a bus functional model. In this lecture we are implementing program of Half Adder using Behavioral Modeling style in VHDL.

Source: chegg.com

Source: chegg.com

VHDL Behavioral Modeling Style. Mixed Modeling Style. For these reasons behavioral modeling is considered highest abstraction level as compared to data-flow or structural models. U uninitialised X unkown - when you drive 0 and 1 together. The VHDL synthesizer tool decides the actual circuit implementation.

Source: vhdlwhiz.com

Source: vhdlwhiz.com

Which of the following is not a type of VHDL modeling. The description is abstract in the sense that it does not directly imply a particular gate-level implementation. In behavioral modeling there are different types of delays and this can create problem in functioning of system. Structural modeling Connection of sub modules. Behavioral style consists of one or more process statements.

Source: researchgate.net

Source: researchgate.net

VHDL Behavioral Modeling Style. Behavioral modeling Explains Behaviour Behavioral modeling is used to execute statements. In Chapter 2 and Chapter 3 we saw various elements of VHDL language along with several examplesMore specifically Chapter 2 presented various ways to design the comparator circuits ie. Describing a circuit at the behavioral level. VHDL Design Styles VHDL Design Styles structural Components and interconnects dataflow Concurrent statements behavioral Sequential statements Registers Shift registers Counters State machines synthesizable.

Source: chegg.com

Source: chegg.com

Modeling refers to the descriptive style we are using to describe our digital system. A behavioral description describes a systems behavior or function in an algorithmic fashion. Data flow modeling Design Equations Data flow modeling can be described based on the Boolean expression. In behavioral modeling sequential execution statements are used. I found the above PDF by googling for VHDL dataflow which reveals many more sources of information.

Source: people.vcu.edu

Source: people.vcu.edu

Read more elaboration about it is given here. Behavioral style consists of one or more process statements. The VHDL behavioral model is widely used in test bench design since the test. The description is abstract in the sense that it does not directly imply a particular gate-level implementation. Behavioral modeling refers to a way to write code more precisely to model your hardware design based on its functionality.

Source: slideshare.net

Source: slideshare.net

There are 4 types of modeling styles in VHDL. Behavioral modeling Explains Behaviour Behavioral modeling is used to execute statements. The VHDL behavioral model is widely used in test bench design since the test. In Chapter 2 and Chapter 3 we saw various elements of VHDL language along with several examplesMore specifically Chapter 2 presented various ways to design the comparator circuits ie. And then Chapter 3 presented various elements of VHDL language which can be used to implement.

Source: people.vcu.edu

Source: people.vcu.edu

Dataflow structural and behavioral. This sums up the structural modeling in VHDL. And this makes it very similar to high-level programming languages in syntax and semantics. And then Chapter 3 presented various elements of VHDL language which can be used to implement. Types of Modeling styles in VHDL.

Source: people.vcu.edu

Source: people.vcu.edu

There are 4 types of modeling styles in VHDL. Use the most optimum method you can think of and let your compiler handle the rest. The VHDL synthesizer tool decides the actual circuit implementation. Behavioral modeling Explains Behaviour Behavioral modeling is used to execute statements. Behavioral style consists of one or more process statements.

Source: slideshare.net

Source: slideshare.net

Mixed Modeling Style. The VHDL behavioral model is widely used in test bench design since the test. Now that we have studied dataflow modeling behavioral modeling and structural modeling styles in VHDL you should know that you can mix all of these styles up when you are defining a circuit. Using dataflow modeling structural modeling and packages etc. It works on Concurrent execution.

Source: slideshare.net

Source: slideshare.net

The VHDL synthesizer tool decides the actual circuit implementation. There are 4 types of modeling styles in VHDL. 2 Behavioral Style of Modelling. Behavioral style is the most abstract style. Behavioral DesignModelling Functional performance is the goal of behavioral modeling Timing optionally.

Source: surf-vhdl.com

Source: surf-vhdl.com

Its like writing the algorithm that solves your problem. Dataflow and structural modeling are used to model combinatorial circuits whereas behavioral modeling is used for both combinatorial and sequential circuits. This sums up the structural modeling in VHDL. VHDL Behavioral Modeling Style. This chapter presents some more such keywords.

Source: researchgate.net

Source: researchgate.net

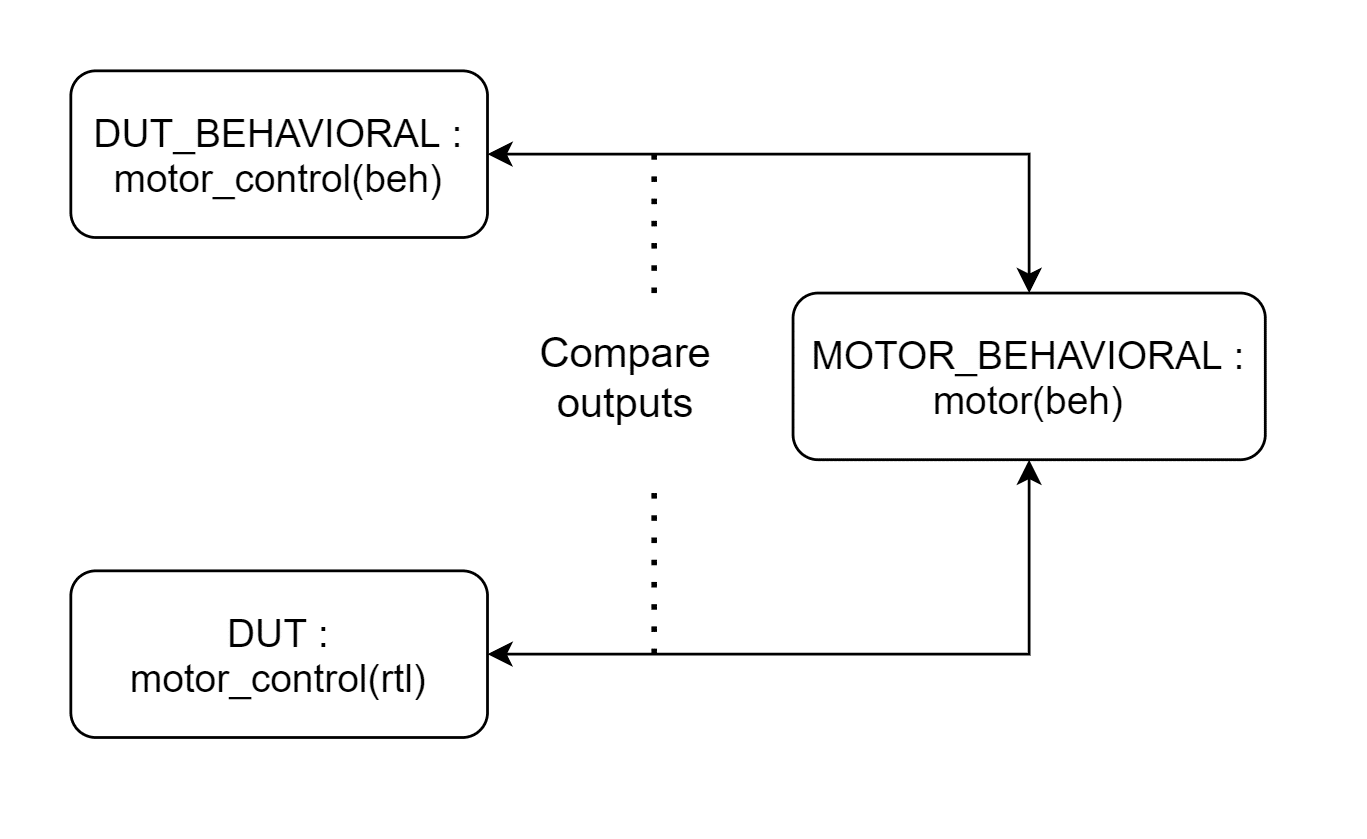

The whole verification flow derived from this approach is depicted in Fig. In Chapter 2 and Chapter 3 we saw various elements of VHDL language along with several examplesMore specifically Chapter 2 presented various ways to design the comparator circuits ie. Could also include code that is completly unsynthesisable - like a bus functional model. Describing a circuit at the behavioral level. The behavioral modeling describes how the circuit should behave.

Source: slidetodoc.com

Source: slidetodoc.com

Data flow modeling Design Equations Data flow modeling can be described based on the Boolean expression. On the other hand The Behavioral modeling in Verilog is used to describe the function of a design in an algorithmic manner so if i want to describe a 2 to 4 decoder in dataflow modeling i. In Chapter 2 2-bit comparator is designed using behavior modeling. Which of the following is not a type of VHDL modeling. This chapter presents some more such keywords.

Source: surf-vhdl.com

Source: surf-vhdl.com

Sometimes zero delay events are used to produce consistent results. Behavioral modeling style is very popular and most prefer. The behavioral modeling describes how the circuit should behave. Mixed Modeling Style. For these reasons behavioral modeling is considered highest abstraction level as compared to data-flow or structural models.

This site is an open community for users to share their favorite wallpapers on the internet, all images or pictures in this website are for personal wallpaper use only, it is stricly prohibited to use this wallpaper for commercial purposes, if you are the author and find this image is shared without your permission, please kindly raise a DMCA report to Us.

If you find this site convienient, please support us by sharing this posts to your own social media accounts like Facebook, Instagram and so on or you can also bookmark this blog page with the title what is behavioral modeling in vhdl by using Ctrl + D for devices a laptop with a Windows operating system or Command + D for laptops with an Apple operating system. If you use a smartphone, you can also use the drawer menu of the browser you are using. Whether it’s a Windows, Mac, iOS or Android operating system, you will still be able to bookmark this website.